# Intelligent Islanding and Seamless Reconnection Technique for Microgrid With UPQC

Shafiuzzaman K. Khadem, Member, IEEE, Malabika Basu, Member, IEEE, and Michael F. Conlon, Member, IEEE

Abstract—A new proposal for the placement, integration, and control of unified power quality conditioner (UPQC) in distributed generation (DG)-based grid connected/autonomous microgrid/microgeneration ( $\mu$ G) system has been presented here. The DG converters (with storage) and the shunt part of the UPQC Active Power Filter (APFsh) is placed at the Point of Common Coupling (PCC). The series part of the UPQC (APFse) is connected before the PCC and in series with the grid. The dc link can also be integrated with the storage system. An intelligent islanding detection and reconnection technique (IR) are introduced in the UPQC as a secondary control. Hence, it is termed as  $UPQC_{\mu G-IR}$ . The advantages of the proposed UPQC<sub>uG-IR</sub> over the normal UPQC are to compensate voltage interruption in addition to voltage sag/swell, harmonic, and reactive power compensation in the interconnected mode. During the interconnected and islanded mode, DG converter with storage will supply the active power only and the shunt part of the UPQC will compensate the reactive and harmonic power of the load. It also offers the DG converter to remain connected during the voltage disturbance including phase jump.

Index Terms—Distributed generation (DG), intelligent islanding detection (IsD), microgrid, power quality, smart grid, unified power quality compensator (UPQC).

#### I. Introduction

THE challenging issues of a successful integration of unified power quality conditioner (UPQC) in a distributed generation (DG)-based grid connected microgeneration ( $\mu$ G) system are primarily: 1) control complexity for active power transfer; 2) ability to compensate nonactive power during the islanded mode; and 3) difficulty in the capacity enhancement in a modular way [1]. For a seamless power transfer between the grid-connected operation and islanded mode, various operational changes are involved, such as switching between the current and voltage control mode, robustness against the islanding detection and reconnection delays, and so on [2], [3]. Clearly, these further increase the control complexity of the μG systems. To extend the operational flexibility and to improve the power quality in grid connected  $\mu$ G systems, a new placement and integration technique of UPQC have been

Manuscript received October 8, 2013; revised March 28, 2014; accepted May 2, 2014. Date of publication June 2, 2014; date of current version April 30, 2015. Recommended for publication by Associate Editor Y.-F. Liu.

S. K. Khadem is with the Department of Civil, Structural and Environmental Engineering, Trinity College Dublin, Dublin 2, Ireland (e-mail: skkhadem@gmail.com).

M. Basu and M. F. Conlon are with the School of Electrical and Electronic Engineering, Dublin Institute of Technology, Dublin 8, Ireland (e-mail: mbasu@dit.ie; michael.conlon@dit.ie).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2014.2326983

proposed in [4], which is termed as  $UPQC_{\mu G}$ . In the  $UPQC_{\mu G}$ integrated distributed system,  $\mu G$  system (with storage) and shunt part of the UPQC are placed at the Point of Common Coupling (PCC). The series part of the UPQC is placed before the PCC and in series with the grid. The dc link is also connected to the storage, if present.

To maintain the operation in islanded mode and reconnection through the UPQC, communication process between the UPQC<sub> $\mu$ G</sub> and  $\mu$ G system is mentioned in [4]. In this paper, the control technique of the presented  $UPQC_{\mu G}$  in [4] is enhanced by implementing an intelligent islanding and novel reconnection technique with reduced number of switches that will ensure seamless operation of the  $\mu$ G without interruption. Hence, it is termed as  $UPQC_{\mu G-IR}$ . The benefits offered by the proposed  $UPQC_{\mu G-IR}$  over the conventional UPQC are as

- 1) It can compensate voltage interruption/sag/swell and nonactive current in the interconnected mode. Therefore, the DG converter can still be connected to the system during these distorted conditions. Thus, it enhances the operational flexibility of the DG converters/µG system to a great extent, which is further elaborated in later

- 2) Shunt part of the UPQC Active Power Filter (APF<sub>sh</sub>) can maintain connection during the islanded mode and also compensates the nonactive Reactive and Harmonic Power (QH) power of the load.

- 3) Both in the interconnected and islanded modes, the  $\mu$ G provides only the active power to the load. Therefore, it can reduce the control complexity of the DG converters.

- 4) Islanding detection and reconnection technique are introduced in the proposed UPQC as a secondary control. A communication between the UPOC and  $\mu$ G is also provided in the secondary control. The DG converters may not require to have islanding detection and reconnection features in their control system.

- 5) The system can even work in the presence of a phase jump/difference (within limit) between the grid and  $\mu$ G.

- 6) Thus, the  $UPQC_{\mu G-IR}$  will have the total control of the islanding detection and reconnection for a seamless operation of  $\mu G$  with a high-quality power service.

This paper has been organized as follows. The working principle of the proposed system is described in Section II. Based on the working principle, some of the design issues and rating selection have been discussed in Section III. Section IV deals with the islanding detection and reconnection techniques in detail. Section V shows the real-time performance study for the proposed control and integration technique that has been verified using real-time simulator in hardware synchronization mode.

#### II. WORKING PRINCIPLE

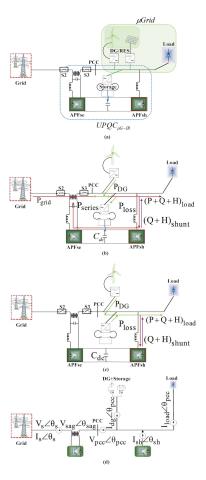

The integration technique of the proposed  $UPQC_{\mu G-IR}$  to a grid connected and DG integrated  $\mu G$  system is shown in Fig. 1(a). S2 and S3 are the breaker switches that are used to island and reconnect the  $\mu G$  system to the grid as directed by the secondary control of the  $UPQC_{\mu G-IR}$ . The working principle during the interconnected and islanded mode for this configuration is shown in Fig. 1(b) and (c). The operation of  $UPQC_{\mu G-IR}$  can be divided into two modes.

#### A. Interconnected Mode

In this mode, as shown in Fig. 1(b), the following holds:

- 1) the DG source delivers only the fundamental active power to the grid, storage, and load;

- the APF<sub>sh</sub> compensates the reactive and harmonic (QH) power of the nonlinear load to keep the Total Harmonic Distortion at the PCC within the IEEE standard limit;

- voltage sag/swell/interruption can be compensated by the active power from the grid/storage through the APF<sub>se,t</sub>. The DG converter does not sense any kind of voltage disturbance at the PCC and hence remains connected in any condition;

- if the voltage interruption/black out occurs, UPQC sends a signal within a preset time to the DG converter to be islanded.

## B. Islanded Mode

In this case, as shown in Fig. 1(c), the following holds:

- the APF<sub>se</sub> is disconnected during the grid failure and DG converter remains connected to maintain the voltage at PCC;

- 2) the APF<sub>sh</sub> still compensates the nonactive power of the nonlinear load to provide or maintain undistorted current at PCC for other linear loads (if any);

- 3) therefore, DG converter (with storage) delivers only the active power and hence does not need to be disconnected from the system;

- 4) the APF<sub>se</sub> is reconnected once the grid power is available

From Fig. 1(a)–(c), it is clear that the UPQC $_{\mu G-IR}$  requires two switches compared with four, as required for UPQC $_{\mu G}$  in [4]. A detail of the switching mechanism is discussed in the controller design section.

#### III. DESIGN ISSUES AND RATING SELECTION

The fundamental frequency representation of the system is shown in Fig. 1(d) and the voltage and current relations are derived in (1) and (2). According to the working principle, the APF $_{se}$  is able to work during voltage interruption/sag/swell up to a certain level before it is islanded. The APF $_{sh}$  always compensates QH power of the load. Therefore, design and rating selection for the APF $_{se}$ , APF $_{sh}$ , and series transformer

Fig. 1. (a) Integration technique of the  $UPQC_{\mu G-IR}$ . Working principle in (b) interconnected mode, (c) islanded mode, and (d) fundamental frequency representation.

together with the sizing of dc link capacitor are very important. These are discussed in the following section:

$$V_{\rm pcc} \angle \theta_{\rm pcc} = V_s \angle \theta_s + V_{\rm sag} \angle \theta_{\rm sag} \tag{1}$$

$$I_{\text{load}} \angle \theta_{\text{load}} = I_s \angle \theta_s + I_{\text{dg}} \angle \theta_{\text{pcc}} + I_{\text{sh}} \angle \theta_{\text{sh}}. \tag{2}$$

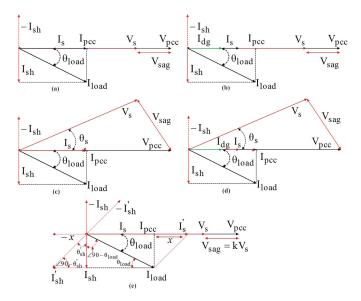

Under any condition assume that  $V_{\rm pcc} = V_{\rm dg} = V_{\rm load}$  and  $\theta_{\rm pcc} = 0^{\circ}$ . The phasor diagrams of the proposed system in different conditions are shown in Fig. 2.

## A. Shunt Part of $UPQC_{uG-IR}$ (APF<sub>sh</sub>)

It is shown in Fig. 2 that for any condition,  $APF_{sh}$  compensates the nonfundamental current of the load by injecting  $I_{sh}$  in quadrature to  $V_{pcc}$ . When voltage sag appears in the supply side,  $APF_{se}$  compensates the sag by injecting the required voltage to maintain the constant voltage and zero-phase at PCC. To complete the task,  $APF_{sh}$  draws additional current from the source, to supply power to the  $APF_{se}$ . The increased source current  $I'_s$  still remains in phase to the  $V_{pcc}$ . But this changes the magnitude and phase angle of the compensating current,  $I'_{sh}$  as an additional active component of current (x) is added to the shunt compensator current now, as shown in Fig. 2(e).

Fig. 2. Phasor diagram of  $UPQC_{\mu G-IR}$  when (a) no DG and  $\theta_s = \theta_{pcc}$ , (b) with DG and  $\theta_s = \theta_{pcc}$ , (c) no DG and  $\theta_s \neq \theta_{pcc}$ , (d) with DG and  $\theta_s \neq \theta_{pcc}$ , and (e) in-phase voltage compensation mode.

In this case

$$I_{s}^{'} = I_{\text{pcc}} + I_{\text{sh}}^{'} \sin(\theta_{\text{sh}}^{'})$$

(3)

$$I'_{\rm sh} = I_{\rm sh}/\cos(\theta'_{\rm sh}). \tag{4}$$

This ultimately increases the current at PCC and thus creates a VA loading impact on the APF<sub>sh</sub>, which is also observed in [6].

## B. Series Part of $UPQC_{uG-IR}$ (APFse)

The APF<sub>se</sub> always appears in series with the grid. In the proposed integration technique when no energy is available from the DG unit and shunt the APF compensates the reactive and harmonic part of the load current, the active fundamental part of the load current ( $I_{loadfp}$ ) flows through the APF<sub>se</sub>. Therefore, the APF<sub>se</sub> must have at least the same current rating as the active load fundamental requirement

$$I_{\text{APF}_{\text{se min}}} = I_{\text{loadfp}}.$$

(5)

From Fig. 2(c) and (d), the general equation for voltage sag compensation by the  $APF_{se}$  can be written as

$$V_{\text{sag}} = \sqrt{V_s^2 + V_{\text{pcc}}^2 - 2V_s V_{\text{pcc}} \text{Cos}(\theta_s - \theta_{\text{pcc}})}.$$

(6)

The voltage rating of the APF<sub>se</sub> should be equal to the highest value of the injected sag voltage, thus

$$V_{\text{APF}_{\text{se,rated}}} = V_{\text{sag,max}} = kV_{\text{load,rated}}.$$

(7)

Assume k is the fraction of  $V_s$  that appears as a voltage sag

$$V_{\text{sag}} = kV_s = kV_{\text{load}}$$

and  $k < 1$ .

Therefore, the VA rating of the APFse, can be calculated as

$$S_{\text{APF}_{\text{se,rated}}} = I_{\text{APF}_{\text{se,rated}}} V_{\text{APF}_{\text{se,rated}}} = k P_{\text{loadf,rated}}. \tag{8}$$

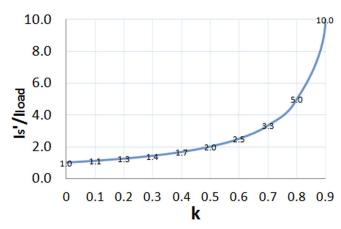

Fig. 3. Relation between source current, load current, and k for voltage sag compensation.

From Fig. 2, the active power transfer through the APF<sub>se</sub> can be calculated for the case when  $I_{dg} = 0$

$$P_{\text{APFse}} = P_{\text{loadf}} \left[ \frac{kV_s}{V_{\text{load}}} \cos(\theta_s - \theta_{\text{pcc}}) \right]. \tag{9}$$

Under stable and in-phase operating conditions, assume that  $\theta_s = \theta_{pcc} = 0$

$$P_{\text{APF}_{\text{se}}} = \frac{k P_{\text{loadf}} V_{s}}{V_{\text{load}}}.$$

(10)

Therefore, during voltage sag compensation, the source current that is transferred through the series transformer of the  $APF_{se}$ , as shown in Fig. 2(e), can be calculated as

$$I_{s}^{'} = \frac{P_{\text{loadf}}}{(1-k)V_{s}} = \frac{1}{(1-k)}I_{\text{loadfp}}.$$

(11)

Thus, the size and VA rating of the series transformer depends on the amount of sag to be compensated. Fig. 3 shows how the source current increases with the value of k. Based on (6)–(11), and for a given value of k, there can be of multiple solutions for  $V_{\rm sag}$ ,  $I_s'$ , and  $P_{\rm APF_{se}}$ . Control strategies are based on the minimization of the energy exchange during compensation or by reducing the voltage rating [5]–[11].

The voltage rating of the  $APF_{se}$  is an important design parameter, as it determines some other characteristics, such as the compensating range, the need to include (and size of) energy storage devices, and the overall size of the series transformer. In addition, losses tend to increase if the voltage rating of the  $APF_{se}$  is increased. Therefore, the voltage injection capability should be chosen as low as necessary to reduce equipment cost and standby losses.

### C. DC Link Capacitor

According to the working principle, the APF<sub>se</sub> should be able to work during a high-sag/swell condition and even in the case of interruption (depending on the interruption time) before it goes to the islanded mode. At this stage, the dc link capacitor should be able: 1) to maintain the dc voltage with minimal ripple in the steady state; 2) to serve as an

energy storage element to supply the nonactive power of the load as a compensation; and 3) to supply the active power difference between the load and source during the sag/swell or interruption period. For a specific system, it is better to consider the higher value of  $C_{\rm dc}$  so that it can handle all of the above conditions. It also helps to get a better transient response and lower the steady-state ripples. According to the calculation in [12], for the proposed system, the required capacitor size will be

$$C_{\rm dc} = \frac{2S_{\rm load} \cdot n \cdot T}{4 \cdot c \cdot V_{\rm dc}^2}$$

(12)

where  $S_{\text{load}}$  is the total VA rating of the load, n is the number of cycles to perform the task, T is the time period, and c is the percentage of  $V_{\text{dc}}$ .

It indicates that the size of the capacitor can be adjusted by the selection of cycles (n) for which the APF<sub>se</sub> will compensate. One of the purposes of the proposed integration technique of the  $UPQC_{\mu G-IR}$  is to maintain smooth power supply during sag/swell/interruption and extend the flexibility of the DG converters operation during interconnected and islanded modes. For the supply continuity, DG storage system has also been introduced. Therefore, a dc link connection between the capacitor and the DG storage has been proposed for the system. It will help to reduce the size of the capacitor and provide power during the sag/interrupt condition. Therefore, the source current will maintain the required load current active component and the additional current will be provided by the DG converters and storage. Thus, it will ultimately help to reduce the rating of the APF<sub>se</sub> converter.

#### IV. CONTROLLER DESIGN

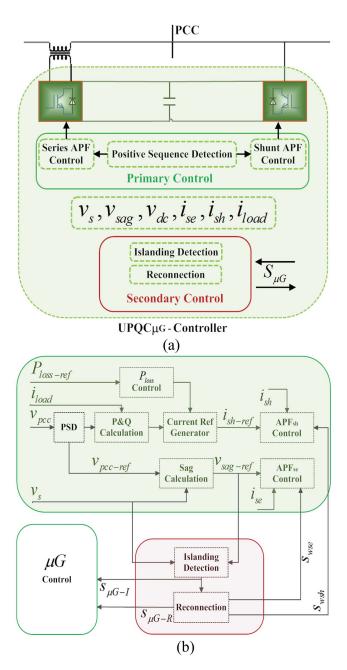

The block diagram of the proposed  $UPQC_{\mu G-IR}$  controller is shown in Fig. 4. It has the same basic functionality as the UPQC controller except for the additional islanding detection and reconnection capabilities. A communication channel (signals transfer) between the proposed UPQC<sub>uG-IR</sub> and the µG is also required for the smooth operation. These signals generation are based on the sag/swell/interrupt/supply failure conditions. This task is performed in Level 2 (secondary control) of the hierarchical control [13]. Level 1 deals with the primary control of the UPQC to perform their basic functions in the interconnected and the islanded mode [14]. The overall integration technique and control strategy are to improve the power quality during interconnected and islanded modes. This involves detecting islanding and reconnection that ensures the DG converter remains connected and supply active power to the load. This reduces the control complexity of the converter as well as the power failure possibility in the islanded mode. The five main elements of the proposed  $UPQC_{uG-IR}$  controller are: 1) positive sequence detection; 2) series part (APF<sub>se</sub>) control; 3) shunt part (APF<sub>sh</sub>) control; 4) intelligent islanding detection (IsD); and 5) synchronization and reconnection (SynRec). As the IsD and SynRec features are new in UPQC, therefore, these have been described in details.

Fig. 4. Block diagram of the  $\mathrm{UPQC}_{\mu\mathrm{G-IR}}.$  (a) Controller. (b) Control algorithm.

#### A. Intelligent Islanding Detection

Considering the future trends toward the smart-grid and  $\mu G$  operation in connection with the distribution grid, the capability of: 1) maintaining connection during grid fault condition; 2) automatically detecting the islanded condition; and 3) reconnecting after the grid fault are the most important features of the  $\mu G$  system. In that case, the placement of APF<sub>se</sub> in the proposed integration method of the system plays an important role by extending the operational flexibility of the DG converter in the  $\mu G$  system.

In addition to the islanding detection, changing the control strategy from current to voltage control may result in serious voltage deviations and it becomes severe when the islanding

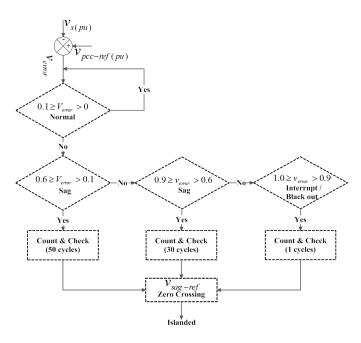

Fig. 5. Algorithm for IsD method in  $UPQC_{\mu G-IR}$ .

detection is delayed in the case of hierarchical control [15]. Therefore, seamless voltage transfer control between the grid-connected and isolated controlled modes is very important [16]–[17]. Both indirect and direct current control techniques are proposed in [2] and [15]–[19] to mitigate the voltage transients in transition mode, but these then increase the control complexity of the  $\mu$ G converters.

In the case of power quality problems, it is reported that more than 95% of voltage sags can be compensated by injecting a voltage of up to 60% of the nominal voltage, with a maximum duration of 30 cycles [20]. Therefore, based on the islanding detection requirement and sag/swell/interrupt compensation, islanding is detected and a signal  $S_{\mu G-I}$ , as shown in Fig. 4(b), is also generated in the proposed UPQC $_{\mu G-IR}$  to transfer it to the DG converters. As the APFse takes the responsibility for compensating voltage sag/swell/unbalance disturbances (depending on the controller), IsD algorithm in the proposed UPQC $_{\mu G-IR}$  can be simple yet quite flexible. On the other hand, it will help to reduce the complexity of islanding detection technique or even can be removed from all the DG converters in a  $\mu$ G system.

Fig. 5 shows a simple algorithm (with example) that has been used to detect the islanding condition to operate the UPQC in islanded mode. The voltage at PCC is taken as the reference and it is always in phase with the source and the DG converters, the difference between the  $V_{\rm pcc-ref}$  (pu) and  $V_s$  (pu) is  $V_{\rm error}$ . This error is then compared with the preset values (0.1–0.9) and a waiting period (user defined n cycles) is used to determine the sag/interrupt/islanding condition. In this example: 1) if  $V_{\rm error}$  is less than or equal to 0.6, then 60% sag will be compensated for up to 50 cycles; 2) if  $V_{\rm error}$  is in between 0.6 and 0.9, then compensation will be for 30 cycles; and 3) otherwise (if  $V_{\rm error} \geq 0.9$ ) it will be interrupt/black out for islanding after 1 cycle.

This signal generation method is simple and can be adjusted for any time length and  $V_{\rm error}$  condition. Thus, the intelligence can be achieved by introducing the operational flexibility of time and control of sag/interrupt compensation before islanding. As the seamless voltage transfer from grid connected to isolated mode is one of the critical tasks in transition period, the transfer is completed at the zero-crossing position of the APF<sub>se</sub>. Therefore, no voltage fluctuation or abrupt conditions occur.

It is to be noted that, this is the first time the algorithm and islanding techniques are introduced in the control part of the UPQC, which are intelligent and flexible in operation. According to Fig. 1, the proper control and operation of the switches are very important for intelligent islanding and seamless reconnection. In that case, this paper presents a topology that represents a step forward compared with the use of intelligent connection agents (ICA) as presented in [16], an additional module named ICA is connected to an existing  $\mu$ G with a number of current sources. The ICA module acts as voltage source to fix the voltage and frequency in islanding mode and is able to guarantee seamless connection/disconnection of the  $\mu$ G from the main grid. The UPQC $_{\mu$ G-IR} presented in this paper is not only able to perform these seamless transitions, but also improve the power quality with some operational flexibility. In addition, the UPQC having a series element (APF<sub>se</sub>) can perform the role of voltage source of the  $\mu$ G, and easily PCC voltage observation-based anti-islanding algorithm can be implemented, as shown in Fig. 5. Notice that using conventional equipment, e.g., in grid connected PV systems, the nondetection zone (NDZ) increases with the number of PV inverters, since they are not able to distinguish between the external grid or other PV inverters output voltage, thus may remain connected for a dangerously long time. With the proposed UPQC control strategy, we can add it in an existing PV plant, and this unit will be the only one responsible of the voltage support and islanding detection, thus being more effective and reducing drastically the NDZ.

#### B. Synchronization and Reconnection

Once the grid system is restored, the  $\mu$ G may be reconnected to the main grid and return to its predisturbance condition. A smooth reconnection can be achieved when the difference between the voltage magnitude, phase, and frequency of the two buses are minimized or close to zero. The seamless reconnection also depends on the accuracy and performance of the synchronization methods [21]–[25]. In case of UPQC<sub> $\mu$ G-IR</sub>, reconnection is performed by the APF<sub>se</sub>. In addition, due to the control of sag/swell by the APF<sub>se</sub>, this UPQC<sub>uG-IR</sub> has the advantage of reconnection even in case of phase jump/difference (up to a certain limit) between the voltage of the utility and at the PCC. This obviously increases the operational flexibility of the  $\mu G$  system with high-power quality. The phase difference limit depends on the rating of the APF<sub>se</sub> and the level of  $V_{\text{sag-max}}$  required for compensation. This limit can be calculated using (1) and Fig. 2. It is also discussed in [26]. Assuming that the possible  $V_{\text{sag-max}} = V_s = V_{\text{pcc}}$ , the

Fig. 6. (a) Position of  $V_s$  and  $V_{\rm pcc}$  for different phase differences to measure the  $V_{\rm sag}$  and  $V_{\rm sag-ref}$ . (b) SynRec.

$\theta_{\text{sag-max}}$  can be found as

$$\theta_{\text{sag-max}} = \cos \left[ \left( \theta_s - \theta_{\text{pcc}} \right) \right]^{-1} = 1/2 = 60^{\circ}.$$

(13)

The relation for the phase difference and magnitude between  $V_s$ ,  $V_{\rm pcc}$ , and  $V_{\rm sag}$  are also shown in Fig. 6(a). It also shows the zero-crossing point of the  $V_{\rm sag-ref}$  depending upon the phase. This zero-crossing detection also indicates the point at which the instantaneous voltage difference between the utility and the PCC becomes zero. Detection of this zero-crossing point and activation of the switches S2 and S3, as shown in Fig. 1, at the same time are the key control of this reconnection method for a seamless transfer from the off-grid to the on-grid condition as well as changing the controller of the DG inverter from voltage to current control mode.

The reconnection method is shown in Fig. 6(b). Conditions for reconnection are set as: 1) assuming the phase difference between the utility grid and DG unit should be within  $\theta_{\text{sag-max}}$ ; 2) instantaneous value of the two bus voltages becomes equal; and 3) these should occur at the zero-crossing condition. Once the utility supply is available after a blackout, a synchronization pulse (generated in reconnection process) is enabled to start synchronization. A simple logic sequence is then created, based on the condition shown in Fig. 6(b), to generate the active pulse for S2 and S3 to return the system in the interconnected mode. At the same time  $S_{\mu G-R}$ , as shown in Fig. 4(b) is also transferred to the  $\mu$ G system for reconnection.

The other advantage is that, IsD and SynRec methods have been carried out as a secondary control in Level 2, i.e., these can also be added in conventional UPQC system as an additional block to convert it to UPQC $_{\mu G-IR}$ . It is to be noted that the proposed UPQC $_{\mu G-IR}$  will be helpful to meet the required advanced grid integration features as mentioned in [27].

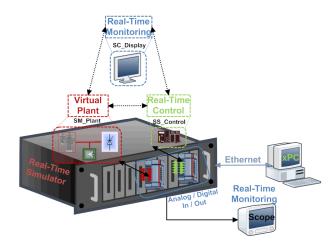

Fig. 7. Real-time simulation structure in SIL configuration with hardware synchronization mode.

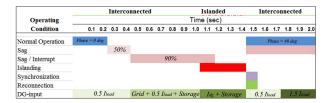

TABLE I

TIMELINE OF THE OPERATING CONDITIONS

#### V. REAL-TIME PERFORMANCE STUDY

With the advancement of technology, real-time performance of any system can be observed using a real-time simulator. Instead of developing the complete actual system at full capacity, either the controller/system can be modeled in software or can be built in hardware or can be a combination of both. In real-time simulation, the accuracy of the computations depends upon the precise dynamic representation of the system and the processing time to produce the results [28].

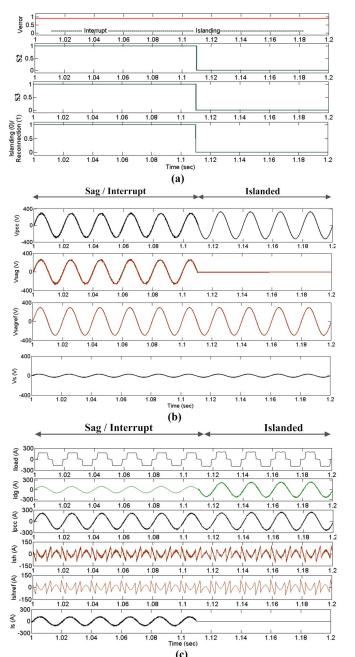

A 3-phase, 3-wire active distribution network (230  $V_{L-N}$ ) with the proposed UPQC $_{\mu G-IR}$  and  $\mu G$ , as shown in Fig. 1, has been developed in the MATLAB using RT-LAB (real-time simulation) tools to observe the performance in the real-time environment. The system is then tested in software-in-loop (SIL), i.e., both the controller and plant are simulated and controlled with the help of real-time communication through external AD/DA cards with appropriate time delay, which is termed as the hardware synchronization mode. Fig. 7 shows the real-time simulation structure in a SIL configuration used to develop the real-time environment by OPAL-RT. The system specifications are as follows,  $UPQC_{\mu G-IR}$  (capability: 100% sag and 100-Amax harmonic current compensation) and the  $\mu$ G (Load: 200 Amax with harmonic 100 Amax and DG: 0.5-1.5 times of load fundamentals). Due to the hardware limitations, switching performance during islanding and reconnection process is obtained in off-line mode. Details of the performance with the simulation results are given below. Off-line simulations have been performed in MATLAB for up to 2 s to observe the complete performance of the system. Table I shows the timeline for the respective operating

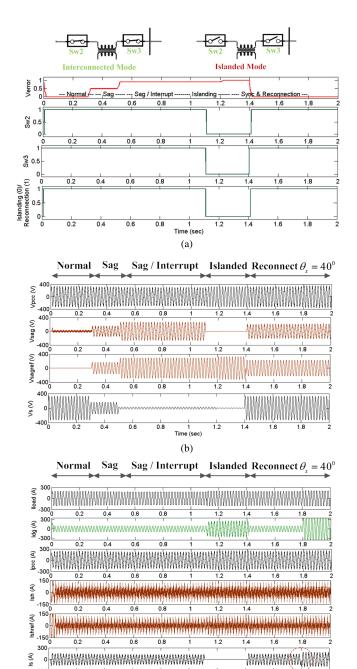

Fig. 8. (a) Switching positions during the operation. (b) Voltage and (c) current waveforms at different conditions and positions in the network.

(c)

conditions, under which the various performance of  $UPQC_{uG-IR}$  has been evaluated.

Fig. 8(a) shows the switch positions (0 for open and 1 for close) during the simulation period from 0 to 2 s where both the interconnected and islanded modes are observed. The performance of the proposed  $UPQC_{\mu G-IR}$  for voltage sag compensation is shown in Fig. 8(b) and harmonic current compensation is shown in Fig. 8(c) based on Table I. Performance during the reverse current flow to the grid due to the high penetration of DG is also shown by the red circle in Fig. 8(c). In general, waveforms are shown for phase A only.

Fig. 9. Performance of APF<sub>sh</sub> (a) forward flow mode, (b) reverse flow mode, APF<sub>se</sub> (compensate voltage sag is 40%), (c) presag, and (d) postsag in reverse flow.

Fig. 10. Performance of APF<sub>se</sub> in forward-reverse flow condition with compensating voltage sag (80%). (a) Dynamic change of  $i_s$ . (b)  $i_s$  increasing by  $i_{\rm dg}$  reverse-forward flow. (c)  $i_s$  decreasing by  $i_{\rm dg}$  forward-reverse flow.

#### A. Interconnected Mode

In this case, two possible mode of operation can be observed: 1) forward and 2) reverse flow. In the forward-flow mode, the available DG power is less than the required load demand. The utility supplies rest of the power to the load. When the DG power becomes higher than the required load demand, the extra energy is transferred to the grid and storage and this is termed the reverse-flow mode. At this stage, the grid current becomes out of phase with the voltage at PCC.

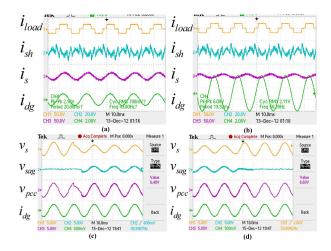

Fig. 9(a) and (b) shows the real-time performance of the APF<sub>sh</sub> part during interconnected mode in compensating the reactive and harmonic current  $(i_{sh})$  generated by the load  $(i_{load})$  in the  $\mu$ G system. Here,  $i_{load}$  contains active, reactive, and

Fig. 11. Performance. (a) Switching (S2 and S3 are open). (b)  $APF_{se}$ . (c)  $APF_{sh}$  during islanded mode.

harmonic part of the total load demand of the  $\mu$ G system. Fig. 9(a) shows the performance in forward flow mode, when  $i_{\rm dg} < i_{\rm loadf}$ . Therefore, additional active current is provided by the grid  $(i_s)$ . Similarly, Fig. 9(b) shows the results for reverse flow mode when  $i_{\rm dg} > i_{\rm loadf}$ . Therefore, additional current from the DG source is transmitted back to the grid and hence  $(i_s)$  phase is reversed.

Fig. 9(c) and (d) shows the response of APF<sub>se</sub> during presag and postsag condition and the performance is obtained in reverse flow mode.

Fig. 10 shows the performance of  $UPQC_{\mu G-IR}$  in dynamic and bidirectional power flow condition during a voltage sag

Fig. 12. Reconnection. (a) Switching (S2 and S3 instances are shown).(b) APF<sub>se</sub> (S3 is closed). (c) APF<sub>sh</sub> (S2 is closed as shown in switching diagram).

(80%) compensation. The performance is obtained with the dynamic change of  $i_{\rm dg}$ , which is reflected in the changes of  $i_{\rm s}$ . From reverse to forward is created by decreasing  $i_{\rm dg}$  during the sag compensation, as shown in Fig. 10(b). Performance in reverse conditions is also shown in Fig. 10(c).

#### B. Islanding Detection

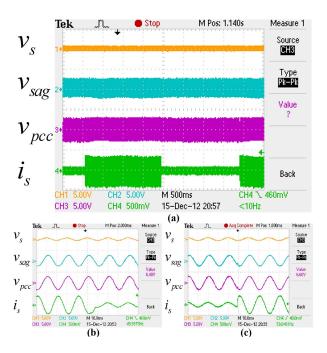

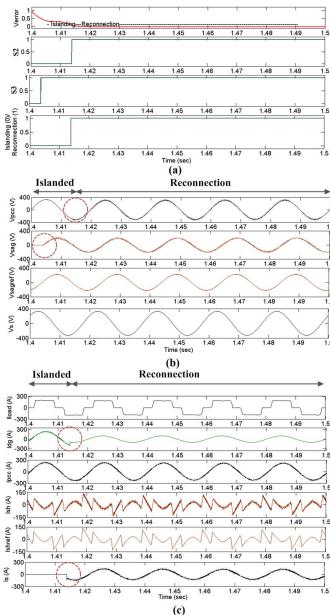

According to the IsD method, the APF<sub>se</sub> compensates the sag for up to 0.6 s (30 cycles) and then the system goes into islanded mode. A utility disconnection is applied at 1.11 s just after completing the 30 cycle count and then detecting the zero-crossing of  $V_{\rm sag-ref}$  where S2 and S3 are opened. At disconnection, the  $\mu$ G operates in islanded mode. At this stage, if the available DG power is lower than the load demand,

the required power is supplied by the storage. If the DG power is higher than the load, then the additional power goes to the storage. The APF<sub>sh</sub> still performs the compensation of nonactive power. Therefore, DG converter does not need to be disconnected or change the control strategy (supply only the fundamental active power) to supply power to the load. Fig. 11 shows the performance of the proposed UPQC $_{\mu G-IR}$  during 1.0–1.2 s, where the islanding is detected just immediately after 1.1 s at zero-crossing detection. The islanding mode is observed between 1.11 and 1.405 s. During this period the APF<sub>se</sub> is disconnected, as shown in Fig. 11(b) where  $V_{\rm sag} = 0$ , and  $I_s$  becomes zero, as shown in Fig. 11(c). The APF<sub>sh</sub> continues to operate, shown in Fig. 11(c), and the load fundamental is met by the DG and storage.

#### C. Reconnection (SynRec)

Fig. 12 shows the signals for reconnection process. To check the performance for one of the worst conditions, the utility grid  $(V_s)$  is powered on at 1.40 s with a 40° out of phase from the PCC. Immediately, the reconnection algorithm is activated and it starts generating active pulses when the phase and amplitude differences are within the required limits. Zero-crossing detection is also shown.  $UPQC_{\mu G-IR}$  sends a reconnection signal to the DG unit. Based on the logic given in Fig. 6, the actual switch S3 and S2 are activated at 1.405 and 1.415 s, respectively. Fig. 12(a) shows that the APF<sub>se</sub> is immediately reactivated and starts operation when  $V_s$  is available and S3 is connected at 1.405 s, as shown by the circle in  $V_{\text{sag}}$  waveform in Fig. 12(b). The power transfer starts when the S2 is closed at 1.415 s, as shown in Fig. 12(c). It is expected that, according to the smooth reclosing condition, no power flow will occur at the point of reclosing. The switching is carried out successfully within the limiting condition as shown in Fig. 12(b). The circle at 1.415 s for  $I_{dg}$  and  $I_s$  in Fig. 12(b) shows the smooth transition from islanded to interconnected mode. The DG inverter also changes its control from voltage to current control mode, but only transfers active fundamental current. The performance of APF<sub>sh</sub> is also uninterrupted during the transition period.

## VI. CONCLUSION

This paper describes a powerful control and integration technique of the proposed  $UPQC_{\mu G-IR}$  in the grid connected μG condition. The real-time performance with off-line simulation has been obtained using MATLAB and RT-LAB in real-time simulator by OPAL-RT. The results show that the UPQC<sub>uG-IR</sub> can compensate the voltage and current disturbance at the PCC during the interconnected mode. Performance is also observed in bidirectional power flow condition. In islanded mode, the DG converters only supply the active power. Therefore, the DG converters do not need to be disconnected or change their control strategy to keep the  $\mu$ G operating in any time with any condition. Islanding detection and seamless reconnection technique by the UPQC<sub>uG-IR</sub> and the dynamic change with bidirectional power flow are validated in real-time for a DG integrated µG System without compromising on power quality.

#### REFERENCES

- S. K. Khadem, M. Basu, and M. F. Conlon, "UPQC for power quality improvement in DG integrated smart grid network—A review," *Int. J. Emerg. Electr. Power Syst.*, vol. 13, no. 1, p. 3, 2012.

- [2] A. Kahrobaeian and Y.-R. Mohamed, "Interactive distributed generation interface for flexible micro-grid operation in smart distribution systems," *IEEE Trans. Sustainable Energy*, vol. 3, no. 2, pp. 295–305, Apr. 2012.

- [3] X. Yu, A. M. Khambadkone, H. Wang, and S. Terence, "Control of parallel-connected power converters for low-voltage microgrid—Part I: A hybrid control architecture," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 2962–2970, Dec. 2010.

- [4] S. K. Khadem, M. Basu, and M. F. Conlon, "A new placement and integration method of UPQC to improve the power quality in DG network," in *Proc. 48th UPEC*, vol. 1. Sep. 2013, pp. 1–6.

- [5] T. Jimichi, H. Fujita, and H. Akagi, "Design and experimentation of a dynamic voltage restorer capable of significantly reducing an energy-storage element," *IEEE Trans. Ind. Appl.*, vol. 44, no. 3, pp. 817–825, May/Jun. 2008.

- [6] M. Basu, S. P. Das, and G. K. Dubey, "Comparative evaluation of two models of UPQC for suitable interface to enhance power quality," *Electr. Power Syst. Res.*, vol. 77, no. 7, pp. 821–830, 2007.

- [7] J. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump," in *Proc.* 16th APEC, vol. 2. 2001, pp. 1267–1273.

- [8] D. M. Vilathgamuwa, A. R. Perera, and S. S. Choi, "Voltage sag compensation with energy optimized dynamic voltage restorer," *IEEE Trans. Power Del.*, vol. 18, no. 3, pp. 928–936, Jul. 2003.

- [9] S. S. Choi, J. D. Li, and D. M. Vilathgamuwa, "A generalized voltage compensation strategy for mitigating the impacts of voltage sags/swells," *IEEE Trans. Power Del.*, vol. 20, no. 3, pp. 2289–2297, Jul. 2005.

- [10] M. R. Banaei, S. H. Hosseini, S. Khanmohamadi, and G. B. Gharehpetian, "Verification of a new control strategy for dynamic voltage restorer by simulation," *Simul. Model. Pract. Theory*, vol. 14, no. 2, pp. 112–125, 2006.

- [11] M. Moradlou and H. R. Karshenas, "Design strategy for optimum rating selection of interline DVR," *IEEE Trans. Power Del.*, vol. 26, no. 1, pp. 242–249, Jan. 2011.

- [12] S. K. Khadem, M. Basu, and M. F. Conlon, "Harmonic power compensation capacity of shunt active power filter and its relationship with design parameters," *IET Power Electron.*, vol. 7, no. 2, pp. 418–430, 2013.

- [13] J. M. Guerrero, J. C. Vasquez, J. Matas, L. G. de Vicuña, and M. Castilla, "Hierarchical control of droop-controlled AC and DC microgrids—A general approach toward standardization," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 158–172, Jan. 2011.

- [14] B. Han, B. Bae, H. Kim, and S. Baek, "Combined operation of unified power-quality conditioner with distributed generation," *IEEE Trans. Power Del.*, vol. 21, no. 1, pp. 330–338, Jan. 2006.

- [15] H. Kim, T. Yu, and S. Choi, "Indirect current control algorithm for utility interactive inverters in distributed generation systems," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1342–1347, May 2008.

- [16] J. Rocabert, G. M. S. Azevedo, A. Luna, J. M. Guerrero, J. I. Candela, and P. Rodríguez, "Intelligent connection agent for three-phase gridconnected microgrids," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 2993–3005, Oct. 2011.

- [17] Z. Yao, L. Xiao, and Y. Yan, "Seamless transfer of single-phase grid-interactive inverters between grid-connected and stand-alone modes," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp. 1597–1603, Jun. 2010.

- [18] F. Gao and M. R. Iravani, "A control strategy for a distributed generation unit in grid-connected and autonomous modes of operation," *IEEE Trans. Power Del.*, vol. 23, no. 2, pp. 850–859, Apr. 2008.

- [19] Y.-R. Mohamed and A. A. Radwan, "Hierarchical control system for robust microgrid operation and seamless mode transfer in active distribution systems," *IEEE Trans. Smart Grid*, vol. 2, no. 2, pp. 352–362, Jun. 2011.

- [20] M. Brenna, R. Faranda, and E. Tironi, "A new proposal for power quality and custom power improvement: OPEN UPQC," *IEEE Trans. Power Del.*, vol. 24, no. 4, pp. 2107–2116, Oct. 2009.

- [21] S.-K. Chung, "A phase tracking system for three phase utility interface inverters," *IEEE Trans. Power Electron.*, vol. 15, no. 3, pp. 431–438, May 2000.

- [22] P. Rodriguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos, and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 584–592, Mar. 2007.

- [23] M. Karimi-Ghartemani and M. R. Iravani, "A method for synchronization of power electronic converters in polluted and variable-frequency environments," IEEE Trans. Power Syst., vol. 19, no. 3, pp. 1263-1270, Aug. 2004.

- [24] H. Geng, D. Xu, and B. Wu, "A novel hardware-based all-digital phase-locked loop applied to grid-connected power converters," IEEE Trans. Ind. Electron., vol. 58, no. 5, pp. 1737-1745, May 2011.

- [25] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase gridconnected power conditioning systems," IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3639–3650, Aug. 2012.

[26] K. S. Khadem, "Power quality improvement of distributed gener-

- ation integrated network with unified power quality conditioner," Ph.D. dissertation, Dept. Elect. Electron. Eng., Dublin Inst. Technol., Ireland, Europe, Jan. 2013.

- [27] F. Blaabjerg and M. Ke, "Future on power electronics for wind turbine systems," IEEE J. Emerg. Sel. Topics Power Electron., vol. 1, no. 3, pp. 139-152, Sep. 2013.

- [28] P. Venne, J. N. Paquin, and J. Bélanger, "The what, where and why of real-time simulation," in Proc. PES General Meeting, Oct. 2010, pp. 37-49.

Malabika Basu (S'99-M'03) received the B.E. and M.E. degrees in electrical engineering from Bengal Engineering College, Kolkata, India, in 1995 and 1997, respectively, and the Ph.D. degree in electrical engineering from IIT Kanpur, Kanpur, India, in

She was a Lecturer with Jadavpur University, Kolkata, from 2001 to 2003. From 2003 to 2006, she was an Arnold F. Graves Post-Doctoral Fellow with the Dublin Institute of Technology, Dublin, Ireland, where she has been a Lecturer since 2006.

She has authored and co-authored more than 60 technical publications in various international journals and conference proceedings. Her current research interests include grid integration of renewable energy sources, power quality conditioners and power quality control and analysis, photovoltaics and wind energy conversion, and smart grids and microgrids.

Shafiuzzaman K. Khadem (S'09-M'13) received the B.Sc. and M.Sc. degrees in applied physics and electronics from the University of Dhaka, Dhaka, Bangladesh, in 1998 and 2000, respectively, and the Ph.D. degree in electrical and electronic engineering from the Dublin Institute of Technology, Dublin, Ireland, in 2013.

He was a Research Associate with the University of Dhaka, Dhaka, from 2001 to 2006, and was later a Lecturer with the Department of Electronics and Telecommunication Engineering, University of

Liberal Arts Bangladesh, Dhaka, for two years. Since 2013, he has been an IRCSET Post-Doctoral Research Fellow with the School of Engineering, Trinity College, University of Dublin, Dublin. His current research interests include power electronics in distribution system, microgrid, power quality, custom power devices, renewable energy, and building energy management

Michael F. Conlon (M'88) received the Diploma and B.Sc. degrees from the Dublin Institute of Technology (DIT), Dublin, Ireland, in 1982, and the M.Eng.Sc. and Ph.D. degrees from University College, Galway, Ireland, in 1984 and 1987, respectively, all in electrical engineering.

He is an Assistant Head of the School of Electrical and Electronic Engineering at DIT, where he is the Director of the Electrical Power Research Centre. He was previously with Monash University and VENCorp, Melbourne, VIC, Australia. His current

research interests include power systems analysis and control applications, power systems economics, integration of wind energy in power networks, analysis of distribution networks, quality of supply, and reliability assessment.